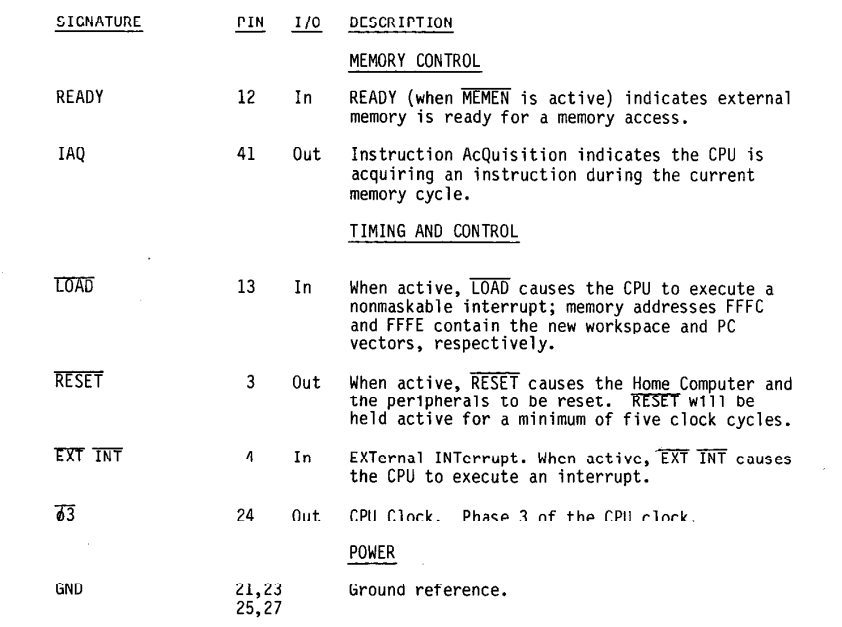

Pin |

Name |

Direction |

Description _ |

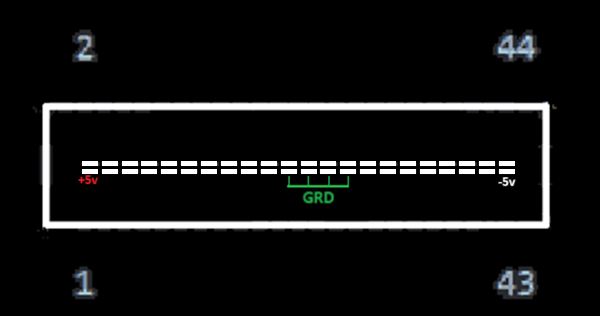

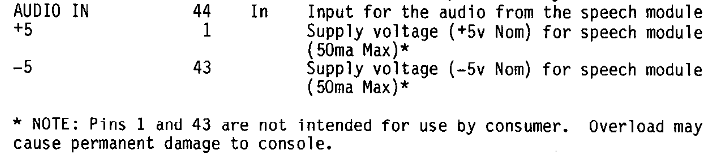

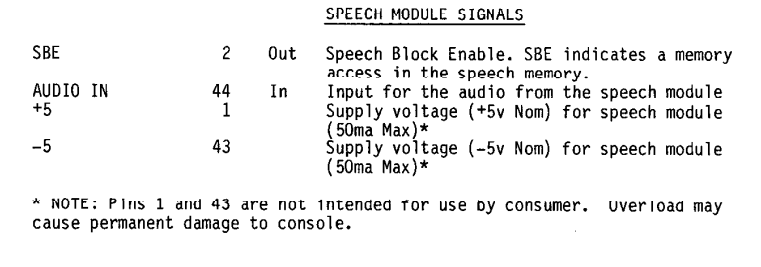

| 1 | VCC (+5V) | - | +5 Volts power supply |

| 2 | SBE | OUT | Low if addr in >9000-94xx (sound port) |

| 3 | RESET* | OUT | System reset (active low) |

| 4 | EXTINT* | IN | External interrupt (active low) |

| 5 | A5 | OUT | Address bus, bit 5 |

| 6 | A10 | OUT | - |

| 7 | A4 | OUT | - |

| 8 | A11 | OUT | - |

| 9 | DBIN (DIN) | OUT | Active high = read memory |

| 10 | A3 | OUT | - |

| 11 | A12 | OUT | - |

| 12 | READY | IN | Active high = memory is ready |

| 13 | LOAD* | IN | Unmaskable interrupt (=> BLWP @>FFFC) |

| 14 | A8 | OUT | - |

| 15 | A13 | OUT | - |

| 16 | A14 | OUT | - |

| 17 | A7 | OUT | - |

| 18 | A9 | OUT | - |

| 19 | A15/CRUOUT | OUT | Address bus, lsb. Also CRU output bit. |

| 20 | A2 | OUT | - |

| 21 | GND | - | Ground |

| 22 | CRUCLK* | OUT | Inversion of TMS9900 CRUCLOCK pin |

| 23 | GND | - | Ground |

| 24 | PHI3* | OUT | Inversion of phase 3 clock |

| 25 | GND | - | Ground |

| 26 | WE* | OUT | Write Enable (derived from TMS9900 WE* pin) |

| 27 | GND | - | Ground |

| 28 | MBE* | OUT | Active low if addr in >4000-5FFF (card ROMs) |

| 29 | A6 | OUT | - |

| 30 | A1 | OUT | - |

| 31 | A0 MSB | OUT | Address bus, bit 0 (most significant bit) |

| 32 | MEMEN* (ME) | OUT | Memory access enable (active low) |

| 33 | CRUIN | IN | CRU input bit to TMS9900 |

| 34 | D7 | IN/OUT | Data bus, bit 7 (least significant) |

| 35 | D4 | IN/OUT | - |

| 36 | D6 | IN/OUT | - |

| 37 | D0 | IN/OUT | Data bus, bit 0 (most significant) |

| 38 | D5 | IN/OUT | - |

| 39 | D2 | IN/OUT | - |

| 40 | D1 | IN/OUT | - |

| 41 | IAQ | IN | Interrupt acknowledged by TMS9900 |

| 42 | D3 | IN/OUT | - |

| 43 | VDD (-5V) | - | -5 Volts power supply |

| 44 | AUDIOIN | IN | To sound generator AUDIO IN pin |